## MorFuzz: Fuzzing Processor via Runtime Instruction Morphing enhanced Synchronizable Co-simulation

Jinyan Xu and Yiyuan Liu, *Zhejiang University;* Sirui He, *City University of Hong Kong;* Haoran Lin and Yajin Zhou, *Zhejiang University;* Cong Wang, *City University of Hong Kong*

https://www.usenix.org/conference/usenixsecurity23/presentation/xu-jinyan

# This paper is included in the Proceedings of the 32nd USENIX Security Symposium.

August 9-11, 2023 • Anaheim, CA, USA

978-1-939133-37-3

## MorFuzz: Fuzzing Processor via Runtime Instruction Morphing enhanced Synchronizable Co-simulation

Jinyan Xu

Zhejiang University

phantom@zju.edu.cn

Haoran Lin

Zhejiang University

haoran\_lin@zju.edu.cn

Yiyuan Liu Zhejiang University yiyuanliu@zju.edu.cn

Yajin Zhou\*

Zhejiang University

yajin\_zhou@zju.edu.cn

Sirui He

City University of Hong Kong

sol.he@my.cityu.edu.hk

Cong Wang

City University of Hong Kong

congwang@cityu.edu.hk

### **Abstract**

Modern processors are too complex to be bug free. Recently, a few hardware fuzzing techniques have shown promising results in verifying processor designs. However, due to the complexity of processors, they suffer from complex input grammar, deceptive mutation guidance, and model implementation differences. Therefore, how to effectively and efficiently verify processors is still an open problem.

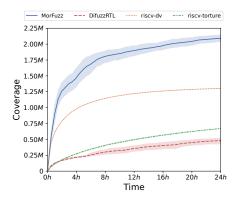

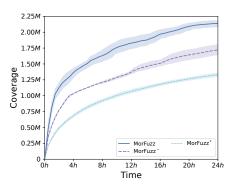

This paper proposes MorFuzz, a novel processor fuzzer that can efficiently discover software triggerable hardware bugs. The core idea behind MorFuzz is to use runtime information to generate instruction streams with valid formats and meaningful semantics. MorFuzz designs a new input structure to provide multi-level runtime mutation primitives and proposes the instruction morphing technique to mutate instruction dynamically. Besides, we also extend the co-simulation framework to various microarchitectures and develop the state synchronization technique to eliminate implementation differences. We evaluate MorFuzz on three popular open-source RISC-V processors: CVA6, Rocket, BOOM, and discover 17 new bugs (with 13 CVEs assigned). Our evaluation shows MorFuzz achieves  $4.4 \times$  and  $1.6 \times$  more state coverage than the state-of-the-art fuzzer, DifuzzRTL, and the famous constrained instruction generator, riscv-dv.

## 1 Introduction

With extensions to improve performance and extend functionality, processor designs are becoming more and more sophisticated. Modern processors are extremely large and complex, typically with billions of transistors and multiple cores. Meanwhile, processors also become increasingly error-prone, and even the latest commodity processors suffer from hardware bugs. For example, Intel discovered 42 errata in their 12th-gen CPUs [13]. Bugs in the processor not only produce incorrect computations (e.g., the infamous Pentium FDIV bug [11] returns inaccurate floating-point division results) but also cause

devastating errors, such as unpredictable system behavior, locking up the machine, and even software security corruptions. The hyper-threading bug [12] can cause data corruption or loss in general-purpose registers, the Barcelona TLB bug [10] and the Pentium F00F bug [11] freeze up the processor, and vulnerabilities like SYSRET bug [15] and memory sinkhole [17] allow unprivileged code escalate into higher privilege. Since hardware bugs are difficult to patch after the chip is manufactured, it is vital to discover bugs in the pre-silicon phase.

Two main methods are proposed to discover hardware bugs automatically: static formal verification [21, 27, 40, 46, 69, 71] and dynamic simulation-based verification. While formal verification methods can thoroughly verify small designs, they are limited by the state explosion problem and fail to scale to large, complex designs such as processors. To automatically maximize the exploration of the state space of the processor under test, researchers proposed two mechanisms, constrained random verification [28, 35, 41, 66] and coverage guided test generation [22, 56, 59, 60], to direct the simulation-based methods to generate better test cases. However, these dynamic methods both require design-specific knowledge to define the generation strategies, which require heavy manual effort.

Recently, fuzzing has become the most popular and effective method in software systems due to the ability to discover unknown vulnerabilities with minimal knowledge [4, 25, 29, 47, 51, 55]. Inspired by the effectiveness of fuzzing, researchers started to apply software fuzzing to processors [6, 7, 30, 32, 33, 37, 39]. Unfortunately, according to our evaluation (§5.3), existing fuzzers are still far from being adopted in practice. Previous efforts fail to effectively and efficiently fuzz processors because of the following three challenges.

First, the input grammar of the processor is complex. Processors usually support many different instructions, each of which has its own unique format. Moreover, these instructions require different types of operands (e.g., integers, floating-point numbers, addresses) to perform meaningful operations, further complicating the input grammar. Existing fuzzers [30, 32, 33] statically generate and mutate instructions, re-

<sup>\*</sup>The corresponding author.

sulting in limited mutation primitives and missing effective semantics. The second challenge is that the control transfer instructions (such as jump and branch instructions) impair the effectiveness of mutations. Existing fuzzers ignore the interference of the input's control flow on the coverage. As a result, valuable mutations may be skipped because of the control transfer instructions and thus incorrectly discarded. And the third issue with existing fuzzers is the implementation differences between models. Almost all previous fuzzers [6, 30, 32, 33] introduce a reference model to check the correctness of the processor. By comparing the state of the processor with that of the reference model, they treat the mismatched states as bugs. However, software reference models are inherently different from hardware, and not all differences are bugs. These false positives caused by implementation differences misguide the fuzzers and prevent them from covering the deep states of the processor.

We address the aforementioned challenges with MorFuzz, a novel processor fuzzer that can detect software triggerable hardware bugs efficiently. MorFuzz addresses the first two challenges by dynamically generating diverse and meaningful instruction streams based on the runtime information. First, MorFuzz introduces a new input structure, the stimulus template, to explore the processor's input space from multiple dimensions. The stimulus template provides primitives to mutate inputs at the processor state, instruction field, and program semantic levels. Second, MorFuzz uses runtime information to morph instructions dynamically. We propose the instruction morphing technique, which collects contextual information from the processor at runtime to mutate instructions with valid formats and meaningful semantics. In addition, since all mutations are executed, the coverage correctly reflects the effect of the mutations, achieving efficient mutation guidance. Finally, MorFuzz eliminates implementation differences through state synchronization. We extend the co-simulation framework to various microarchitectures and add state synchronization support. This allows MorFuzz to identify the source of the differences and synchronize the hardware state to the reference model to eliminate legal differences.

We have implemented a prototype of MorFuzz on RISC-V architecture and evaluated it on three real-world open-source processors: CVA6 [68], Rocket [1], and BOOM [70]. These processors under evaluation cover various microarchitectures, from simple in-order cores to complex out-of-order superscalar cores. Our evaluation shows that MorFuzz achieves at most  $4.4 \times$  and  $1.6 \times$  more state coverage than the state-of-theart processor fuzzer, DifuzzRTL, and the famous constrained instruction generator, riscv-dv, respectively. In terms of performance, MorFuzz achieves the coverage that DifuzzRTL takes 24 hours to achieve in about 30 minutes and takes about 2.4 hours to achieve the coverage that riscv-dv takes 24 hours to complete. MorFuzz identified 17 new bugs in total, 13 of which are assigned with CVE numbers, and all of these bugs are confirmed by the respective communities.

In summary, this paper makes the following contributions:

- We propose a novel processor fuzzing approach that uses runtime information to dynamically generate meaningful input and efficiently guide mutation.

- We present the design and implementation of MorFuzz, a processor fuzzing framework that can efficiently detect software triggerable hardware bugs. MorFuzz achieves  $4.4\times$  and  $1.6\times$  higher coverage than the state-of-theart processor fuzzer, DifuzzRTL, and the famous constrained instruction generator, riscv-dv, respectively.

- MorFuzz is a generic RISC-V processor fuzzer that is compatible with various microarchitectures. We evaluate MorFuzz on three popular real-world RISC-V processors (CVA6, Rocket, BOOM) and totally discover 17 new bugs (with 13 CVEs assigned).

- To facilitate the community and future research, we release the source code of MorFuzz at https://github. com/sycuricon/MorFuzz.

## **Background**

#### **RISC-V Instruction Set Architecture** 2.1

The RISC-V instruction set architecture (ISA) is an opensource reduced instruction set architecture that has gradually become popular in industry and academia. It is composed of a base integer instruction set and a set of optional instruction-set extensions. The standard extensions contain integer multiplication and division, atomic memory operations, single/doubleprecision floating-point, and compressed instructions. In addition, the control and status register (CSR) instruction extension provides control over the privileged architecture, and the instruction-fetch fence extension is designed to synchronize the instruction memory.

| 24         | 19                                                                         |                                                                                                     | 14                                                                                                                                                                  | 1    | 1   | ε   | 3      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| rs2        |                                                                            | rs1                                                                                                 | fund                                                                                                                                                                | ct3  | rd  |     | opcode | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ₹   |

| imm        |                                                                            | rs1                                                                                                 | fund                                                                                                                                                                | ct3  | rd  |     | opcode |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ı   |

| rs2        |                                                                            | rs1                                                                                                 | fund                                                                                                                                                                | ct3  | imr | n   | opcode |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S   |

| rs2        |                                                                            | rs1                                                                                                 | fund                                                                                                                                                                | ct3  | imr | n   | opcode | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3   |

| imm        |                                                                            |                                                                                                     |                                                                                                                                                                     |      | rd  |     | opcode | ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | J   |

| imm        |                                                                            |                                                                                                     |                                                                                                                                                                     |      | rd  |     | opcode |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | J   |

| 15 12      | 11                                                                         |                                                                                                     | 6                                                                                                                                                                   | 4    | 1 0 |     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct4     | _                                                                          | d/rs1                                                                                               | rs                                                                                                                                                                  | s2   | ор  | CR  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct3 imm |                                                                            | d/rs1                                                                                               | in                                                                                                                                                                  | nm   | ор  | CI  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct3     |                                                                            |                                                                                                     | rs                                                                                                                                                                  | s2   | ор  | css |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct3     |                                                                            |                                                                                                     |                                                                                                                                                                     | rd'  | ор  | CIW |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct3     | imm                                                                        | rs1'                                                                                                | imm                                                                                                                                                                 | rd'  | ор  | CL  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct3     | imm                                                                        | rs1'                                                                                                | imm                                                                                                                                                                 | rs2′ | ор  | cs  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct6     |                                                                            | rd'/rs1'                                                                                            | funct2                                                                                                                                                              | rs2′ | ор  | CA  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct3     | imm                                                                        | rs1'                                                                                                | in                                                                                                                                                                  | nm   | ор  | СВ  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| funct3     |                                                                            |                                                                                                     | 1                                                                                                                                                                   |      | ор  | CJ  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|            | rs2 rs2 imm imm  15 12 funct3 funct3 im funct3 funct3 funct3 funct3 funct3 | rs2 rs2 imm imm  15 12 11 funct4 rfunct3 imm funct3 imm funct3 imm funct3 imm funct6 imm funct6 imm | rs2 rs1 rs2 rs1 rs2 rs1 rs2 rs1 rs2 rs1 imm imm  15 12 11 funct4 rd/rs1 funct3 imm funct3 imm funct3 imm funct3 imm funct3 imm rs1' funct6 rd'/rs1' funct3 imm rs1' | rs2  | rs2 | rs2 | rs2    | rs2         rs1         funct3         rd         opcode           rs2         rs1         funct3         imm         opcode           rs2         rs1         funct3         imm         opcode           rs2         rs1         funct3         imm         opcode           imm         rd         opcode           imm         rd         opcode           funct4         rd/rs1         rs2         op         CR           funct3 imm         rd/rs1         imm         op         CI           funct3 imm         rs2         op         CS         CS           funct3 imm         rs1' imm         rd'rs1' op         CL         CL           funct3 imm         rs1' imm         rs2' op         CS         CS           funct6 rd'rs1' funct2 rs2' op         CA         CA           funct3 imm         rs1' imm         op         CB | rs2 |

Figure 1: RISC-V instruction formats.

RISC-V instructions currently have two valid lengths. Except for the 16-bit compressed instructions, all other instructions are 32-bit width. Figure 1 shows all 15 instruction formats, each consisting of multiple fields. The format of the 32-bit width instruction is determined by the opcode field, while the op and the funct fields determine that of the 16-bit width instruction. Currently, there are two categories of instruction fields. The first category is opcode related fields. The funct and opcode fields are used to determine the instruction's operation, also known as the opcode. The lower two bits of the opcode field and the op field are used to determine the length of the instruction. The funct fields and the other bits of the opcode field are used to determine the opcode type. Typically, instructions with similar functions have the same opcode field and are distinguished by the funct fields. The second category is the operand related fields. The imm and rs fields are designed to provide the operands. The rs fields are used to select the source registers, and the imm fields are used as the immediate number. And the rd fields are used to control the destination register, where the result of the instruction is written back.

## 2.2 Processor Verification

Unlike software, hardware cannot be easily patched once manufactured. To avoid pre-silicon bugs from escaping to post-silicon, verification is performed throughout the development process. Statistically, about 56% of the project time is spent on verification [23].

## 2.2.1 Typical Processor Verification

The processor is a finite state machine, and its state includes the microarchitectural state and the architectural state. The microarchitectural state represents the implementation-related internal state that is transparent to the outside of the processor. In contrast, the architectural state holds the state of a program (e.g., the memory and the general-purpose registers) and is consistent across the same ISA. We denote the implementation of the processor design under test (DUT) as a function  $f_{DUT}$ ,  $S_{DUT}$  denotes the state of the DUT in current cycle. At each cycle, the processor generates the next state  $S'_{DUT}$  based on the current state  $S_{DUT}$  and the external input I (i.e., instructions):  $f_{DUT}(I, S_{DUT}) \rightarrow S'_{DUT}$ . The task of processor verification is to check whether the implementation function  $f_{Spec}$  defined in the specification.

Researchers deploy two main methods to verify hardware designs: static formal verification [21, 27, 40, 46, 69, 71] and dynamic simulation-based verification. As formal verification is limited to scale to complex designs [16], simulation-based verification is more prevalent in practice. The simulation-based verification uses tailored input to simulate the DUT and verify whether the output of the DUT meets expectations.

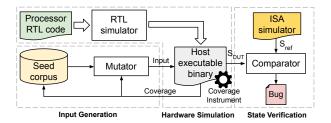

Figure 2: Hardware fuzzer workflow.

The typical simulation-based verification method involves the following three phases. First, the test case generator randomly generates instruction streams based on constraints [28, 35, 41, 66] or coverage [22, 56, 59, 60]. Next, the RTL simulator [14, 52, 65] translates the RTL code of the processor under test into a software model. The simulator then compiles the software model with its test harness (containing the input interpreter) into a host executable binary file. The simulation is performed by executing the binary file, and during the simulation, the input is translated into the bus transactions that are recognized by the DUT. Finally, the correctness of the DUT's behavior during the simulation is checked by verifying the external visible architectural state of the processor due to the difficulty of checking an abstract implementation. A golden reference model is introduced to execute the same input, and the correctness of the DUT can be determined by comparing the architectural state of the DUT  $S_{DUT_{arc}}$  and the reference model  $S_{REF_{arc}}$ .

## 2.2.2 Processor Fuzzing

The typical processor verification method described above is limited by the quality of the generated test cases, struggling to cover corner cases. Fuzzing has recently become a popular testing technique for automatically detecting software security vulnerabilities. Driven by the success of fuzzing, researchers have recently proposed to apply it to processor verification [6, 7, 30, 32, 33, 37, 39]. Figure 2 illustrates the general workflow of the existing processor fuzzing frameworks, which also consist of three phases. In the input generation phase, the fuzzer generates instruction streams using the seeds and mutates the instruction streams based on the coverage of the previous round. DifuzzRTL [30] uses the static analysis technique to generate instructions with required operands, and TheHuzz [33] optimizes mutations according to its optimal weights. In the hardware simulation phase, the RTL code of the DUT is also translated into the host executable binary file. During the simulation, the fuzzer uses the instruments in the hardware to collect the coverage of the current input. Existing fuzzers have designed various coverage matrices, such as mux coverage [37], control register coverage [30], and hardware behavior coverage [33]. In the state verification phase, the fuzzer extracts the DUT's architectural state and

```

start:

call init_regs

2

call init_page_table

addi x2, x4, -935

la x2, 186

jalr x20, 0(x2)

10

csrrw x6, satp, x5

11

12

blt x25, x6, exit

13

14

exit:

15

call signature

```

Figure 3: Example test case generated by DifuzzRTL.

then compares it with a reference model (e.g., an ISA simulator) and reveals the mismatches as bugs. However, previous fuzzers simply port software fuzzing to the traditional verification flow while ignoring the challenges of processor fuzzing. According to our statistics in Figure 8, the performance of the state-of-the-art processor fuzzer, DifuzzRTL [30], is even worse than using randomly generated test cases.

#### 2.3 **Challenges of Processor Fuzzing**

We use the test case (Figure 3) generated by the state-ofthe-art processor fuzzer DifuzzRTL [30] as an example to articulate the challenges of processor fuzzing and analysis why previous fuzzers fail to effectively and efficiently fuzz processors. In the first three lines, the test case initializes the execution environment. Lines 4 to 14 are instructions used to fuzz the functionality of the processor. Each label is a test point, and DifuzzRTL typically generates about 180 test points on average in one test case. In the end, the test case dumps the architectural state of the processor to memory as the signature and exits the simulation (line 16).

Complex Input Grammar. The processor's behavior is determined not only by the external input instructions I but also by its current state  $S_{DUT}$ . Since the state of the processor is accumulated from previous instructions, instruction sequences also affect the state of the processor. And the instruction itself also contains two variables, the opcode and the operand, both of which might take on legal or illegal values. Based on these multi-dimensional parameters, processor inputs also have complex semantics, and an instruction only performs meaningful operations with valid operands in a particular execution environment. Existing fuzzers fail to generate diverse and meaningful instruction streams limited by static generation and unidimensional mutation. For example, DifuzzRTL uses approximate static analysis to select operands, while TheHuzz randomly mutates fields ignoring semantics.

Deceptive Mutation Guidance. Unlike software fuzzing,

the input of the processor fuzzing contains control transfer instructions and exceptions. For this reason, the generated instructions are not guaranteed to be executed, so the coverage actually reflects the effect of the executed instructions rather than the effect of the generated instructions. Unfortunately, existing fuzzers all choose the latter, making the coverage misleading to the mutation. For example, the jalr instruction on line 8 jumps from 12 to 186, causing all instructions from 13 to 185 to be skipped. Suppose the skipped instructions contain some valuable mutations, and the executed instructions do not contribute to the coverage. The fuzzer will consider all these mutations unhelpful and will eventually discard them. As a result, the coverage incorrectly guides the fuzzing toward an ineffective direction.

Model Implementation Differences. Existing fuzzers use an ISA simulator as the reference model to detect hardware bugs. However, the ISA simulator is only a functional model of the processor, and there are some inherent differences compared with the actual hardware. For example, the ISA simulator is cycle inaccurate and lacks peripheral simulation. Therefore the two models will get mismatched values when accessing these registers. Another source of the differences is the indeterminateness in the specification. The RISC-V specification does not restrict the implementation, so potentially multiple behaviors are allowed. For instance, the property of the CSR (e.g., satp) usually is "Write Any Read Legal", which means that even if the same value is written to the CSR, the value readout may differ depending on the implementation (line 11). Unfortunately, these differences are legal in the specification. And even worse, since the state verification phase is offline, these differences can cause the two models' control flows to diverge. For instance, the DUT uses the mismatched value to execute the branch instruction at line 13. If the DUT and the simulator do not perform consistent branch behavior, it will lead to completely mismatched subsequent traces, resulting in meaningless execution.

**Inefficient Execution**. The duplicated instruction streams have no contribution to the coverage. For example, before the fuzzing payload in the test case is executed, the fuzzer spends considerable time loading the test case into the DUT's memory and waiting for the DUT to execute several initialization functions (e.g., init regs, init page table) to set up the environment. However, DifuzzRTL can only access the DUT through limited ports provided by the test harness, and once the simulation starts, the fuzzer has no control over the control flow of the test case. Due to the poor controllability of the DUT, the time-consuming initialization process is repeatedly executed without any improvement in coverage, which results in ineffective fuzzing.

## Design

MorFuzz is a novel coverage-guided processor fuzzer that can efficiently detect software triggerable hardware bugs. In

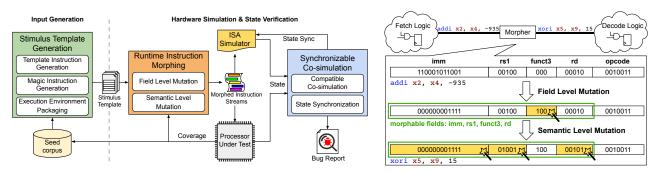

Figure 4: Overview of MorFuzz.

Figure 5: Example of instruction morphing.

this section, we first give an informal verification scope of MorFuzz and then elaborate on the design details.

## 3.1 Verification Scope

Unlike previous fuzzers [7, 32, 37, 58] that focused on bugs triggered by specific hardware signals, MorFuzz is designed to detect architecture functional bugs triggered by software. Specifically, MorFuzz focuses on bugs triggered by specific combinations of instructions that cause the processor's behavior to deviate from the ISA specification. Therefore, the processor's behaviors under any privilege need to be verified, and behaviors that are undefined or unconstrained in the specification are out of our verification scope. MorFuzz will trust the high privilege levels it relies on and use simplified firmware to provide the required functionality when testing the processor's behavior at low privilege levels. In addition, transient execution bugs caused by microarchitecture mistakes are out of our scope [42, 64].

## 3.2 Architecture Overview

The core idea behind MorFuzz is to dynamically mutate instructions based on the runtime feedback. In summary, MorFuzz leverages the following techniques to resolve the aforementioned challenges (§2.3): the stimulus template, the instruction morphing, and the synchronizable co-simulation.

Stimulus Template (§3.3). Unlike existing fuzzers that directly generate instruction streams as the stimulus, MorFuzz uses a stimulus template to generate diverse and meaningful instruction streams. The stimulus template provides multilevel runtime mutation primitives, including processor state level, instruction field level, and program semantic level, thereby comprehensively exploring the input space of the processor. In addition, the stimulus template also introduces the ability for the fuzzer to communicate with the DUT to manage the control flow of test cases. Therefore, the fuzzer can accurately control the DUT to skip duplicate instructions and focus on the instruction sequences it is interested in.

**Instruction Morphing** (§3.4). Instruction morphing only mutates those instructions that are going to be executed instead

of mutating instructions indiscriminately like existing fuzzers. Instruction morphing is a dynamic instruction mutation technique that accurately reflects the effect of the mutations, and thereby the coverage can effectively guide the fuzzer. And instruction morphing uses runtime information to mutate opcodes and operands, ensuring that the morphed instructions maintain valid field format and meaningful semantics. Besides, instruction morphing is performed on binary instructions, which makes it easier for MorFuzz to generate corner cases that assembly language cannot represent, thus greatly increasing the efficiency in exploring the input space.

Synchronizable Co-simulation (§3.5). MorFuzz synchronizes the legal differences to address the implementation differences between models. During the simulation, MorFuzz uses a simulator to co-simulate with the DUT, and compares the architectural state of the DUT and the simulator after each instruction is executed to check the correctness. Co-simulation can also allow MorFuzz to locate which instruction caused the mismatched state accurately. Based on this, MorFuzz can further analyze whether the difference is legal and synchronize the correct state from the DUT to the simulator, thus eliminating the mismatch. Benefiting from the synchronizable co-simulation framework, MorFuzz can automatically mitigate the implementation differences and allow the simulator to co-simulate synchronously with the DUT, thus directing the fuzzer to cover more depth states.

Overview. The overall workflow of MorFuzz is depicted in Figure 4. First, MorFuzz uses seeds to generate the stimulus templates. Then, MorFuzz dynamically morphs the template based on the runtime information and executes morphed instruction streams simultaneously on the DUT and the simulator. Finally, after each instruction is executed, MorFuzz compares the architectural state of the two models. After MorFuzz analyzes the mismatches, the legal difference states are synchronized to the simulator, and the others are reported as potential bugs.

## 3.3 Stimulus Template Generation

We design a new structure for the test case, the stimulus template, to provide runtime mutation primitives for processor

state and instructions. The stimulus template consists of two parts: the runtime morphable fuzzing payload and the readonly fuzzing execution environment. The fuzzing payload contains the runtime mutation primitives, and the fuzzing execution environment is the system firmware responsible for providing a software execution environment that allows the DUT to execute the fuzzing payload continuously.

**Template Instruction Generation**. Template instructions are blank payload instructions for instruction morphing, which provide mutation primitives for the instruction field and the program semantic at runtime. During the generation, the template instruction acts like a placeholder, only containing the fields that determine the length of the instruction to calculate the memory layout of the stimulus template. The other fields are temporarily filled with dummy values, which MorFuzz will replace with meaningful values based on the contextual information later during the simulation. MorFuzz generates template instructions at block granularity and designs different testing blocks to cover the various hardware functional modules of the processor. A set of sequence patterns are manually constructed in each testing block to constrain the instruction types of each template instruction in the block to achieve the desired test points. Under the constraints of the sequence pattern, each testing block is randomly filled with a bunch of template instruction sequences with special semantics. In addition, the sequence patterns also expose the DUT's internal state by inserting watchpoint instructions at specific locations to enhance observability. For example, MorFuzz inserts instructions to read the floating-point exception flag CSR after the floating-point instruction sequence to check whether the exception flag is set correctly.

Magic Instruction Generation. MorFuzz instruments magic instructions in the prologue of each testing block as the processor state runtime mutation primitives. The magic instructions are the load instructions that access a random number generator mounted in the test harness. During the simulation, the DUT can atomically randomize the general-purpose registers by accessing the generator. The DUT can specify the generated data type by accessing different address offsets of the generator, including integers, floating-point numbers, addresses, page table entries, etc. The random number generator can generate not only random numbers but also particular corner values (e.g., illegal addresses, maximum and minimum in integers, INF and NaN in floating-point numbers). This significantly improves the possibility of covering corner cases and increases fuzzing stress.

Instruction Shuffle. To further increase the sequence level randomness, we also perform a randomized perturbation of the order of all instructions in the fuzzing payload at the end of the generation, called instruction shuffle. Although some watchpoints will be sacrificed, shuffling instructions mix up adjacent testing blocks, increasing the diversity of instruction sequences and further producing more processor states.

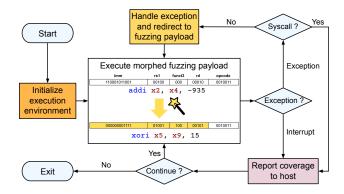

Execution Environment Packaging. MorFuzz integrates a

powerful fuzzing execution environment into the stimulus template. First, the fuzzing execution environment is responsible for setting up the execution environment, such as initializing general-purpose registers and memory, configuring address translation mode, and switching to the target privilege level. Second, morphed instructions inevitably trigger exceptions, so the fuzzing execution environment is required to be able to handle the exceptions to avoid crashing the execution. And third, the fuzzer manages the control flow of the stimulus template through the fuzzing execution environment. After executing the scheduled fuzzing payload, the fuzzing execution environment communicates with the fuzzer, and the fuzzer decides whether to continue the simulation based on the reported coverage.

## 3.4 Runtime Instruction Morphing

When the hardware simulation begins, MorFuzz uses instruction morphing to morph the template instructions to generate diverse and meaningful instruction streams. To mutate the instruction being executed, MorFuzz inserted a morpher into the DUT. The morpher is a logic block inserted in the circuit, which does not affect the processor's functionality. Typically, it is placed on the wire that connects the processor fetch unit and the decode unit. Figure 5 illustrates the workflow of the morpher. First, the morpher hijacks the instruction fetched from memory. Next, the morpher decodes the instruction and performs field level mutation on morphable opcode related fields. And then, the morpher uses the contextual information to generate operand related fields with good semantics. Lastly, the morphed instruction is sent back to the decoder unit. From the view of the processor, the instruction fetched from memory magically turns into another different instruction.

Field Level Mutation. Field level mutation is a structured binary mutation approach that ensures the mutated instructions remain a valid format. To avoid subsequent mutations from destroying the structure of the instruction, the morpher chooses to generate an instruction similar to the hijacked template instruction instead of producing a completely different instruction. Therefore, the morpher does not mutate the fields that determine the instruction format and length, e.g., the opcode field. When a new template instruction arrives, the morpher first decodes the instructions and determines which fields are morphable. Next, the morpher randomly selects valid opcodes defined in the specification to replace the opcode related fields in the morphable fields. For instance, in Figure 5, by morphing the funct3 field, the morpher mutates an addi instruction into a xori instruction. And finally, the morpher passes the half-finished instruction and the list of morphable fields to the subsequent mutation process.

Semantic Level Mutation. To make the morphed instructions close to real-world usage scenarios, the morpher not only generates the operand related fields randomly but also combines contextual information to mutate the semantics.

Figure 6: Stimulus template runtime workflow.

First, the morpher generates valid address offsets based on the current program counter and address space. During the simulation, the morpher senses DUT's address translation mode and maps the memory layout in the stimulus template into the current address space. When generating an immediate number related to the address (e.g., the imm field of the branch instructions), the morpher calculates address offset based on the current program counter and mapped target address, thus ensuring that the morphed immediate number is meaningful.

Second, the morpher maintains a type pool of general-purpose registers to provide operands with the desired type. For memory load and store instructions, they require that the base address register field rs1 must point to a register containing an address. In order to generate meaningful rs fields, the morpher keeps track of the data types (including address and general data) in the general-purpose registers to provide the correct operand type. To simplify type tracing, MorFuzz does not trace the data flow but only marks the type of the destination register as its obtained data type when executing a magic instruction. If another normal instruction writes that destination register again, the register will lose its type.

Third, the morpher uses a sliding window to record the destination register field rd of instructions still being executed in the pipeline. The morpher can use the registers in the sliding window as the rs and rd fields for subsequent template instructions to generate instructions containing pipeline hazards, such as read-after-write and write-after-write. Therefore, MorFuzz is also able to generate inputs matching the microarchitectural details of the DUT spontaneously.

Notice that the morpher would still try illegal cases with a small probability because the input space out of the specification is also a significant source of bugs, such as the illegal opcodes bugs B1 and the illegal operands bugs B4.

**Diverse and Meaningful Instruction Streams**. Finally, with the help of the stimulus template, MorFuzz morphs template instructions to produce diverse and meaningful instruction streams on the fly. As Figure 6 shown, the DUT starts execution from the initialization function in the fuzzing execution environment and jumps to the fuzzing payload. While execut-

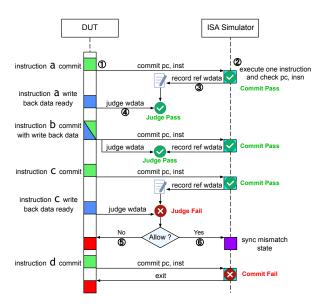

Figure 7: MorFuzz state verification flow.

ing the morphed instructions, if the DUT triggers an exception, the exception handler in the fuzzing execution environment will try to handle the exception. Whether or not the handler successfully handles the exception, the handler redirects the DUT back to the fuzzing payload. A unique system call is triggered when the DUT reaches the boundary of the fuzzing payload, notifying the fuzzer to collect the current coverage and fix the program counter. By evaluating the coverage, if the fuzzer is interested in the input, it controls the DUT to return to the fuzzing payload again. Otherwise, the fuzzer will terminate the simulation and generate a new stimulus template. In addition, to avoid the DUT from falling into dead loops, MorFuzz also monitors the coverage. If the coverage does not increase for a period of time, the fuzzer will raise an interrupt to stop the simulation. In summary, the fuzzer can control the DUT to continuously execute diverse and meaningful instruction streams in a loop without additional initialization, thus significantly improving the fuzzing performance.

## 3.5 Synchronizable Co-simulation

MorFuzz applies an online co-simulation approach for state verification, using an ISA simulator running in parallel with the DUT as the reference model. The ISA simulator and the DUT execute the same inputs, so the correctness of the DUT's state can be checked by comparing their states after each instruction is executed.

Compatible Co-simulation. The existing work has assumed that the write-back data is always ready when the DUT commits instructions. However, this assumption is not always true due to the microarchitectural differences between processors. For example, Rocket [1] supports delayed write-back, which means the write-back data of long-latency instructions (e.g.,

multiply and divide, floating-point instructions) may not be ready at the commit stage.

To accommodate different microarchitectures, MorFuzz abstracts the state comparison process into two stages, the commitment stage and the judgment stage. More specifically, we use the instruction a-d in Figure 7 as an example. Assuming that the write-back data is not ready when the DUT commits the instruction a. In the commitment stage, the DUT first commits its program counter and the executed instruction (1). Once the simulator receives the commit request, it executes the next instruction and then checks if the executed instruction is consistent with the one committed by the DUT (2). If the check passes, the simulator records its reference write-back data to the scoreboard (3). The judgment stage starts after the write-back data of the instruction a is ready. MorFuzz compares the write-back value with the reference value in the scoreboard to determine whether the instruction is executed correctly (4). The instruction b shows the case where the commit stage and the judgment stage fire simultaneously, MorFuzz is compatible with this case. When mismatched behavior is detected, MorFuzz reports the potential bug and exits the simulation (e.g., instruction d, c-(5)).

State Synchronization. As discussed in §2.3, not all mismatched differences are bugs. According to our statistics in Figure 10, these implementation differences are triggered with high probability. Although MorFuzz can stop the simulation in time at the mismatched instruction through online state verification, exiting the simulation means that the DUT loses the currently accumulated state, making it difficult for the fuzzer to penetrate the deep states of the processor. Therefore, MorFuzz proposes a synchronizable co-simulation approach to automatically eliminate implementation differences, allowing the DUT to synchronize its state to the reference model to sustain the simulation. For instance, suppose the instruction c accesses a peripheral register, and the judgment stage fails because the simulator lacks a corresponding peripheral simulation. MorFuzz can determine whether the mismatched difference is legal by analyzing the accessed physical address on the simulator. If legal, MorFuzz synchronizes the hardware state to the simulator (6) and otherwise reports it as a potential bug ((5)). In addition, MorFuzz can also synchronize external events, such as interrupts, to the simulator. By automatically synchronizing mismatched states, MorFuzz allows the simulation to execute deeper rather than stopping prematurely due to false positives.

## **Implementation**

In this section, we discuss several relevant implementation details of MorFuzz. We first describe the stimulus template generator, followed by the fuzzing framework for processor simulation and verification. The prototype we implemented is based on the RISC-V 64-bit architecture.

#### 4.1 **Stimulus Template Generation**

The stimulus template generator consists of 2.6K lines of python code and 1.3K lines of assembly and C code. We define a 128-bit seed to generate the stimulus template. The seeds determine the fuzzing execution environment and instruction extensions to be tested, control the weight of different testing blocks, seed the random number generator, and set the intensity of the instruction shuffle.

**Testing Block.** MorFuzz generates different types of testing blocks based on the weights in the seed. The higher the weight of the testing block in the seed, the more likely it is to be generated. We have designed seven types of testing blocks to cover various hardware functional modules of the DUT, including integer arithmetic test, floating-point arithmetic test, CSR test, memory operation test, atomic memory operation test, system operation test, and custom extension test. And control transfer instruction is placed at the end of each testing block to chain them together.

Fuzzing Execution Environment. We extended the testing environment provided by the official RISC-V testing repository [54] as the fuzzing execution environment. The fuzzing execution environment initializes the processor and configures the environment, such as the available instruction extensions, the address translation mode and page table, and the runtime privilege level. During the simulation, the fuzzing execution environment is placed in a non-morphable physical area and is responsible for handling exceptions and interrupts with the highest privilege level. In addition to managing the execution environment, the fuzzing execution environment also provides interfaces to fuzz the system environment, e.g., we provide a series of page table randomization functions to mutate page table entries and evict mapped pages.

## 4.2 Processor Fuzzing

We use the starship SoC generator [57] to generate the test harness for the processor under test, including the on-chip interconnect system and the memory model that saves the compiled stimulus template. The hardware test harness of the DUT is implemented using about 2K lines of Chisel and 500 lines of Verilog. And we extract the core logic of the official RISC-V ISA simulator, the spike [53], as the reference model to check the correctness of the DUT's behavior. We use about 2.5K lines of C++ code to complete the morpher and the co-simulation framework.

Instruction Morphing. The morpher is implemented as software logic embedded in hardware. It uses the Verilog DPI interface to interact with the hardware, i.e., monitor the processor's internal state, hijack fetched instructions, and return morphed instructions. The morpher performs field-aware mutation on fetched instructions and only replaces the wires between the fetch unit and the decode unit, which ensures that the morphed instructions keep the instruction fetch offset

consistency with the pipeline front-end and does not require modification of the pipeline back-end. Therefore the morpher does not introduce unwanted effects.

In addition, to ensure that the reference model can perform the same morphing as the DUT, the morpher maintains a morphing map, using the instruction before morphing and its address as the key and the morphed instruction as the value. Thus instruction morphing does not introduce false positives, and both models are always able to execute deterministic and identical morphed instructions.

Synchronization Prerequisite. We have strictly defined the rules to approve state synchronization. A difference must meet the following three prerequisites to be considered a legal difference. First, only instructions involving operations beyond the verification scope are allowed to perform subsequent steps. This limits the types of instructions that are allowed to trigger state synchronization to CSR instructions and memory operation instructions. Second, the control flow information of the DUT must pass the commitment stage check. If the DUT incorrectly approves access to privileged registers or reserved address space, an exception will be thrown on the simulator side due to insufficient permissions. MorFuzz will prevent synchronization after observing a program counter violation during the commitment stage. Third, mismatched write-back values are limited to the CSR WARL fields defined in the specification or the data reading from peripheral addresses outside the specification. With further fine-grained checks, MorFuzz can ensure that all synchronized differences are out of our verification scope.

Hardware Simulation. We use an industry-standard commercial tool, Synopsys VCS [14], to simulate hardware RTL designs, but MorFuzz does not rely on features that are exclusive to commercial tools. All hardware modules are translated to Verilog code and then compiled into a host executable binary through the Synopsys VCS RTL simulator.

Hardware Coverage Matrix. MorFuzz is compatible with the coverage matrices proposed by existing designs, and we use the same control register coverage to facilitate comparison with DifuzzRTL [30]. The control register is the register whose value is used for any multiplexers' select signal. We implemented the same FIRRTL [31] pass to instrument all the control registers. The instrumented circuits count the different states triggered in the module and sum up the count as the final coverage. The control register coverage is clock-sensitive and reflects the hardware state better than other coverage matrices. Note that the coverage is only used to evaluate the effect of inputs and mutations, and achieving high coverage in the DUT does not mean that the design is bug-free.

## **Evaluation**

In this section, we evaluate the effectiveness of MorFuzz in various aspects. In summary, we aim to answer the following four questions:

- **RO 1.** How effective is MorFuzz in discovering previously unknown bugs in real-world processors? (§5.2).

- RQ 2. How does MorFuzz perform compared with previous methods in exploring the states of processors? (§5.3)

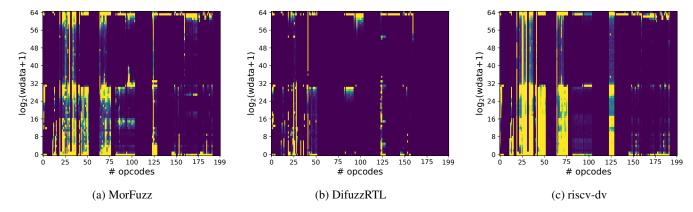

- RQ 3. Are the instructions generated by instruction morphing valid and diverse? (§5.4)

- RQ 4. How do the instruction morphing and the state synchronization contribute to the effectiveness of our fuzzer? (§5.5)

#### 5.1 **Experimental Setup**

We conducted the experiments on a 48-core Intel Xeon Silver 4214 processor with 256GB RAM. We ran each experiment for 24 hours and repeated the experiment five times. We fuzzed three popular processors in the RISC-V community to demonstrate that MorFuzz is compatible with different RISC-V microarchitectures. All processors are capable of booting and running Linux, and the configurations of each processor are summarized in Table 1.

CVA6 [68] is an open source 64-bit in-order RISC-V processor core written in SystemVerilog. Although its six-stage pipeline is single-issue, it has independent internal execution functional units. Thus it is able to commit multiple instructions simultaneously. It also has been taped out in 22nm technology and runs at up to 1.7GHz.

Rocket [1] is a five-stage, single-issue, in-order scalar processor written in Chisel [2]. Rocket's pipeline is ingeniously designed to support the delayed write-back, allowing the processor to commit long latency instructions without carrying write-back data. Rocket is the world's first RISC-V processor open sourced by UC Berkeley and is still actively supporting new extensions (e.g., hypervisor [50] and cryptography [49]). Moreover, it has been taped out dozens of times and extensively verified by academia and industrial groups.

**BOOM** [70] is the third generation of the Berkeley Out-of-Order Machine (BOOM). It is an out-of-order superscalar processor also written in Chisel. Unlike the above in-order cores, BOOM has a more sophisticated microarchitecture, and we used the triple-issue LargeBoom configuration for the experiment. The latest BOOM has been verified on FPGA and achieves better performance than its predecessor.

Table 1: Summary of the cores used for evaluation.

| Feature        | CVA6     | Rocket   | BOOM         |

|----------------|----------|----------|--------------|

| ISA            | RV64GC   | RV64GCHX | RV64GCX      |

| Pipeline Stage | 6        | 5        | 10           |

| Issue Order    | In-order | In-order | Out-of-order |

| Lines of code  | 24K      | 99K      | 339K         |

#### 5.2 **Bugs Found in Real-World Processors**

During the evaluation, MorFuzz found 17 new bugs and two already known bugs in total. Our results demonstrate that Mor-Fuzz is capable of finding unknown bugs that are ignored by previous extensive verification conducted by both academia and industrial groups. Moreover, we take responsible disclosure. We report all bugs found to the community using the suggested channels and assist the developers in fixing 9 of them. We also apply CVE identifiers for all newly discovered bugs, and 13 bugs are assigned with CVE numbers. Since MorFuzz does not explicitly target security property violations, direct exploitation of most discovered bugs is to launch denial-ofservice attacks. For example, bug B10 prevents the processor from executing crafted instructions correctly, the wrong type generated by bug B13 makes the kernel fail to handle exceptions properly and triggering bug B18 shuts down the system. In general, it is difficult to evaluate the exact security impacts of functional bugs without real-world exploitation scenarios. Recent attacks have shown that even faulty computation results can compromise security isolation [5, 34, 43–45]. We list all the bugs found by MorFuzz in Table 2 together with their corresponding common weakness enumerations (CWEs) to show their potential security implications.

We also compare the average bug reproduction time in Table 3. We select similar bugs reported by previous work to highlight the efficiency improvement over the previous processor fuzzer and instruction generator. In the case of bug B7, MorFuzz triggers the problem significantly faster than riscv-torture and DifuzzRTL. Additionally, since we included binary-level mutations, we may effectively trigger bugs that previous methods failed to cover, such as B8.

Next, we describe in detail the bugs found by MorFuzz. Depending on the complexity, these bugs can be classified into three categories: instruction decoder related, CSR state related, and complex logic bugs. We identify these bugs with the latest RISC-V ISA specification [62, 63].

## 5.2.1 Instruction Decoder Related Bugs

The first category of bugs is decoder bugs caused by the rare corner format of a single instruction. Previous fuzzers mutate inputs at the instruction level, only generating assembly instructions with valid formats. MorFuzz performs binary-level field-aware mutation, enabling more efficient exploration of unexpected instruction formats.

Bug B1. According to the specification, the rcon field of aes64ks1i should not greater than 0xA. When executing an aes64ks1i with roon field greater than 0xA, Rocket does not throw an illegal instruction exception.

Bug B6. By setting the rm field in the floating-point instruction, programmers can specify the rounding mode. BOOM can execute floating-point instructions with illegal rm fields (such as 5 or 6) without raising exceptions.

**Bug B8**. In the specification, sfence. vma has a zero rd field. CVA6 considers illegal sfence.vma is valid when its rd field is mutated to a non-zero value.

Bug B9. The CVA6 decoder behaves incorrectly when executing dret with a non-zero rd field, which should be zero according to the specification. CVA6 handles this invalid dret as if it were a legal dret.

Bug B10. For forward compatibility, implementations must ignore rd fields in fence. i/fence, and standard software must clear them. When executing a non-standard fence.i/fence with a non-zero rd field, CVA6 throws an exception.

## 5.2.2 CSR State Related Bugs

CSR state bugs require first setting the CSR to a specific state and then inducing the buggy behavior through instruction sequences. MorFuzz is able to generate instruction sequences that meet the above requirements with the guidance of sequence patterns.

Bug B2. In Rocket, the custom extension illegal signal incorrectly uses vector extension status. Due to this bug, the valid custom extension instruction may fail to execute.

Bug B3. vsstatus.xs field is writable in Rocket. The xs field summarizes the extension context status, and according to the specification, it is read-only.

**Bug B7**. If we set the frm to DYN (or an invalid value), any floating-point instruction whose rm field is set to DYN should raise an illegal instruction exception. Nonetheless, BOOM executes these instructions without raising an exception.

Bug B11. When the mstatus.fs field is set to dirty, the mstatus.sd field in CVA6 does not update immediately. This bug may cause the contents of the floating-point registers to be lost during the context switch.

Bug B12. CVA6 writes the binary instruction of the ebreak to the mtval/stval register when it executes an ebreak. According to the specification, mtval/stval should contain the faulting virtual address if it is written with a non-zero value when a breakpoint exception occurs. And the ecall also for the same reason.

Bug B18. Spike's mcontrol. action component contains an incorrect mask, which is 0x3f, while this field only has 4 bits width. If users attempt to set the sizelo field next to it, an illegal action will be saved, forcing the program simulation to crash abruptly.

## **Complex Logic Bugs**

The remaining bugs are not concentrated in specific hardware functional modules and require numerous instructions with specific semantics to prepare a buggy environment, we collectively call them logic bugs. MorFuzz monitors the internal runtime states of the DUT to dynamically morph instructions and randomize operands, greatly enhancing the semantics of

Table 2: A list of bugs discovered by MorFuzz.

| Processor | Bug Description                                                                       | CVE/Issue ID   | CWE      | New Bug      | Confirmed    | Fixed                     |

|-----------|---------------------------------------------------------------------------------------|----------------|----------|--------------|--------------|---------------------------|

|           | B1: Treat aes64ksli with rcon greater than 0xA as valid                               | CVE-2022-34632 | CWE-327  | ✓            | ✓            | $\overline{}$             |

| Rocket    | <b>B2</b> : Error in condition of the rocc_illegal signal                             | Issue #2980    | CWE-1281 | $\checkmark$ | ✓            | $\checkmark$              |

|           | <b>B3</b> : The vsstatus.xs is writable                                               | CVE-2022-34627 | CWE-732  | $\checkmark$ | ✓            | $\checkmark$              |

|           | B4: Incorrect exception type when a PMA violation                                     | CVE-2022-34636 | CWE-1202 | ✓            | ✓            |                           |

| BOOM      | <b>B5</b> : Incorrect exception type when a PMP violation                             | CVE-2022-34641 | CWE-1198 | $\checkmark$ | ✓            |                           |

| воом      | <b>B6</b> : Floating-point instruction with invalid rm field does not raise exception | Issue #458     | CWE-391  |              | ✓            |                           |

|           | B7: Floating-point instruction with invalid frm does not raise exception              | Issue #492     | CWE-391  |              | ✓            |                           |

|           | B8: Crafted or incorrectly formatted sfence.vma instructions are executed             | CVE-2022-34633 | CWE-1242 | ✓            | ✓            | $\overline{\hspace{1cm}}$ |

|           | B9: Crafted or incorrectly formatted dret instructions are executed                   | CVE-2022-34634 | CWE-1242 | ✓            | ✓            | $\checkmark$              |

|           | B10: Non-standard fence instructions are treated as illegal                           | CVE-2022-34639 | CWE-1209 | $\checkmark$ | ✓            | $\checkmark$              |

|           | B11: The mstatus.sd field does not update immediately                                 | CVE-2022-34635 | CWE-1199 | $\checkmark$ | ✓            |                           |

| CVA6      | B12: The value of mtval/stval after ecall/ebreak is incorrect                         | CVE-2022-34640 | CWE-755  | $\checkmark$ | ✓            |                           |

| CVAO      | B13: Incorrect exception type when a PMA violation                                    | CVE-2022-34636 | CWE-1202 | $\checkmark$ | ✓            |                           |

|           | <b>B14</b> : Incorrect exception type when a PMP violation                            | CVE-2022-34641 | CWE-1198 | $\checkmark$ | ✓            | $\checkmark$              |